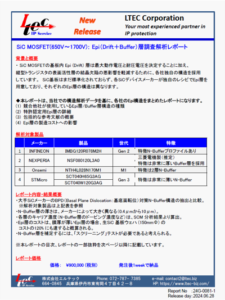

SiC MOSFET(650V~1700V): Epi(Drift+Buffer)層調査解析レポート

背景と概要

・ SiC MOSFETの基板内 Epi (Drift) 層は最大動作電圧と耐圧電圧を決定することに加え、縦型トランジスタの表面活性層の結晶欠陥の悪影響を軽減するために、各社独自の構造を採用しています。 SiC基板はまだ標準化されておらず、各SiCデバイスメーカーが独自のレシピでEpi層を用意しており、それぞれのEpi層の構造は異なります。

◆本レポートは、当社での構造解析データを基に、各社のEpi構造をまとめたレポートになります。

(1)競合他社が使用しているEpi層/Buffer層構造の種類

(2)特許認定用Epi層の詳細

(3)包括的な参考文献の概要

(4)Epi層の製造コストへの影響

解析対象製品

| メーカー | 製品 | 世代 | 特徴 | |

| 1 | INFINEON | IMBG120R078M2H | Gen 2 | 特徴N-Bufferプロファイルあり |

| 2 | NEXPERIA | NSF080120L3A0 | 三菱電機製(推定) 特徴は非常に厚いBuffer層を採用 |

|

| 3 | Onsemi | NTH4L028N170M1 | M1 | 特徴は2層N-Buffer |

| 4 | STMicro | SCT040H65G3AG | Gen 3 | 特徴は非常に薄いN-Buffer |

| SCT040W120G3AG |

レポート内容・結果概要

・大手SiCメーカーのBPD(Basal Plane Dislocation:基底面転位)対策N-Buffer構造の抽出と比較。

※解析対象製品は上記表を参照

・N-Buffer層の厚さは、メーカーによって大きく異なる(0.4μmから10μm)。

・各層のキャリア濃度(N-Buffer層のドーピング濃度など)は、SCM 分析結果より算出。

・Epi層のコストは、膜厚が厚いEpi層の場合、生SiC 基板ウェハ (150mmΦ) の

コストの120% にも達すると概算される。

・N-Buffer層を補足するには、「スクリーニング」テストが必要であると考えられる。

※本レポートの目次、レポートの一部抜粋を次ページ以降に記載しています。

レポート価格

価格:¥900,000 (税別) 発注後1weekで納品

レポートパンフレット

24G-0081-1-Br-L2 SiC MOSFET(650V~1700V): Epi(Drift+Buffer)層調査解析レポート(Release)

・その他当社リリースレポートは こちら